# SN54155, SN54156, SN54LS155A, SN54LS156, SN74155, SN74156, SN74LS155A, SN74LS156 DUAL 2-LINE TO 4-LINE DECODERS/DEMULTIPLEXERS SDLS057 – MARCH 1974 – REVISED MARCH 1988

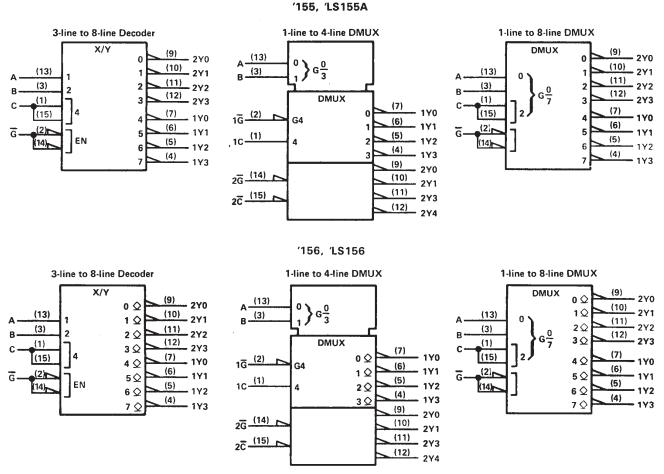

- Applications: Dual 2-to 4-Line Decoder Dual 1-to 4-Line Demultiplexer 3-to 8-Line Decoder 1-to 8-Line Demultiplexer

- Individual Strobes Simplify Cascading for Decoding or Demultiplexing Larger Words

- Input Clamping Diodes Simplify System Design

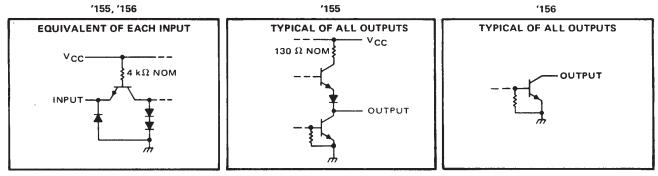

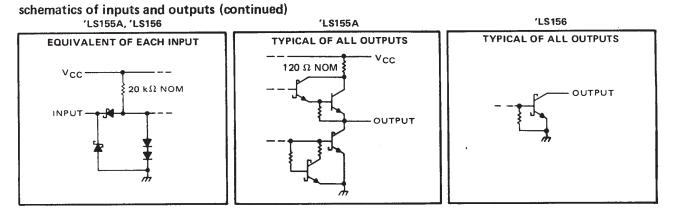

- Choice of Outputs: Totem Pole ('155, 'LS155A) Open-Collector ('156, 'LS156)

|                           | TYPICAL AVERAGE   | TYPICAL<br>POWER |  |  |

|---------------------------|-------------------|------------------|--|--|

| TYPES                     | PROPAGATION DELAY |                  |  |  |

|                           | 3 GATE LEVELS     | DISSIPATION      |  |  |

| <b>'1</b> 55, <b>'156</b> | 21 ns             | 125 mW           |  |  |

| 'LS155A                   | 18 ns             | 31 mW            |  |  |

| 'LS156                    | 32 ns             | 31 mW            |  |  |

#### description

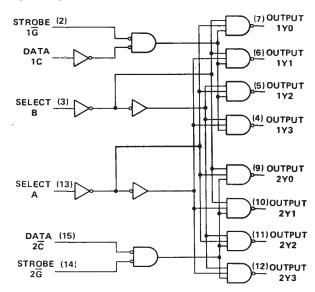

These monolithic transistor-transistor-logic (TTL) circuits feature dual 1-line-to-4-line demultiplexers with individual strobes and common binary-address inputs in a single 16-pin package. When both sections are enabled by the strobes, the common binary-address inputs sequentially select and route associated input data to the appropriate output of each section. The individual strobes permit activating or inhibiting each of the 4-bit sections as desired. Data applied to input 1C is inverted at its outputs and data applied at 2C is not inverted through its outputs. The inverter following the 1C data input permits use as a 3-to-8-line decoder or 1-to-8-line demultiplexer without external gating. Input clamping diodes are provided on all of these circuits to minimize transmission-line effects and simplify system design.

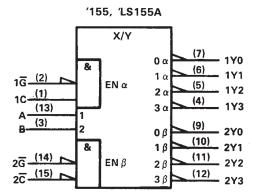

#### logic symbols (2-line to 4-line decoder)<sup>†</sup>

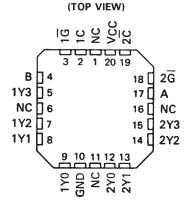

SN54155, SN54156, SN54LS155A, SN54LS156 . . . J OR W PACKAGE SN74155, SN74156 . . . N PACKAGE SN74LS155A, SN74LS156 . . . D OR N PACKAGE

### (TOP VIEW)

| 1C<br>1G<br>B<br>1Y3<br>1Y2<br>1Y1<br>1Y0 | <b>1</b><br>2<br>3<br><b>4</b><br>5<br><b>6</b><br>7 | U16<br>15<br>14<br>13<br>12<br>11 |   | V <u>C</u> C<br>2 <u>C</u><br>2 <u>G</u><br>A<br>2 <u>Y</u> 3<br>2 <u>Y</u> 2<br>2 <u>Y</u> 1 |

|-------------------------------------------|------------------------------------------------------|-----------------------------------|---|-----------------------------------------------------------------------------------------------|

| 1Y0                                       |                                                      | 10                                | 5 | 2Y1                                                                                           |

| GND                                       |                                                      | 9                                 | 5 | 2Y0                                                                                           |

# SN54LS155A, SN54LS156 . . . FK PACKAGE

NC - No internal connection

<sup>†</sup>These symbols are in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12. For alternative symbols for other applications, see the following page.

Pin numbers shown are for D, J, N, and W packages.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1988, Texas Instruments Incorporated

# SN54155, SN54156, SN54LS155A, SN54LS156, SN74155, SN74156, SN74LS155A, SN74LS156 **DUAL 2-LINE TO 4-LINE DECODERS/DEMULTIPLEXERS** SDLS057 - MARCH 1974 - REVISED MARCH 1988

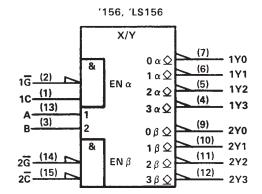

## additional logic symbols (alternatives)<sup>†</sup>

<sup>†</sup>These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for D, J, N, and W packages.

## schematics of inputs and outputs

# SN54155, SN54156, SN54LS155A, SN54LS156, SN74155, SN74156, SN74LS155A, SN74LS156 **DUAL 2-LINE TO 4-LINE DECODERS/DEMULTIPLEXERS**

SDLS057 - MARCH 1974 - REVISED MARCH 1988

### logic diagram (positive logic)

#### FUNCTION TABLES 2-LINE-TO-4-LINE DECODER **OR 1-LINE-TO-4-LINE DEMULTIPLEXER**

|          |          | INPUTS       |            | OUTPUTS |     |     |     |  |

|----------|----------|--------------|------------|---------|-----|-----|-----|--|

| SEL<br>B | ECT<br>A | STROBE<br>1G | DATA<br>1C | 1Y0     | 111 | 1¥2 | 1¥3 |  |

| X        | х        | н            | X          | н       | н   | н   | н   |  |

| L        | L        | L            | н          | Ł       | н   | н   | н   |  |

| L        | н        | L            | (н         | н       | L   | н   | н   |  |

| н        | L        | L            | н          | н       | н   | L   | н   |  |

| н        | н        | L            | н          | н       | н   | н   | L   |  |

| х        | x        | x            | Lι         | н       | н   | н   | н   |  |

|          |          | INPUTS |            | OUTPUTS |     |     |     |  |

|----------|----------|--------|------------|---------|-----|-----|-----|--|

| SEL<br>B | ECT<br>A | STROBE | DATA<br>2C | 2Y0     | 2Y1 | 2Y2 | 2Y3 |  |

| х        | х        | н      | ×          | н       | н   | н   | Н   |  |

| L        | L        | L      | L          | L       | н   | н   | н   |  |

| L        | н        | L      | L          | н       | L   | н   | н   |  |

| н        | ε        | L      | L          | н       | н   | L   | н   |  |

| н        | н        | L      | L          | н       | н   | н   | L   |  |

| х        | x        | x      | н          | н       | н   | н   | н   |  |

#### FUNCTION TABLE 3-LINE-TO-8-LINE DECODER OR 1-LINE-TO-8-LINE DEMULTIPLEXER

| INPUTS |   | OUTPUTS |                   |     |     |     |     |     |     |     |     |

|--------|---|---------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| SELECT |   | т       | STROBE<br>OR DATA | (0) | (1) | (2) | (3) | (4) | (5) | (6) | (7) |

| C†     | 8 | A       | G‡                | 270 | 2Y1 | 272 | 2Y3 | 1Y0 | 1Y1 | 172 | 1¥3 |

| х      | Х | Х       | н                 | н   | н   | н   | н   | н   | н   | н   | н   |

| L      | L | L       | L                 | L   | н   | н   | н   | н   | н   | н   | н   |

| L      | £ | н       | L                 | н   | Ł   | н   | н   | н   | н   | н   | н   |

| L      | н | L       | L                 | н   | н   | L   | н   | н   | н   | н   | н   |

| L      | н | н       | L                 | н   | н   | н   | Ł   | н   | н   | н   | н   |

| н      | L | L       | L                 | н   | н   | н   | н   | Ł   | н   | н   | н   |

| н      | ι | н       | ι                 | н   | н   | н   | н   | н   | L   | н   | н   |

| н      | н | L       | L                 | н   | н   | н   | н   | н   | н   | Ł   | н   |

| н      | н | н       | L                 | н   | н   | н   | н   | н   | н   | н   | L   |

<sup>†</sup>C = inputs 1C and  $2\overline{C}$  connected together

$\ddagger \overline{G} = inputs \ 1\overline{G} \ and \ 2\overline{G} \ connected \ together$

H = high level, L = low level, X = irrelevant